# Delay Model Study of Single Ended Ring Oscillator (SERO)

Shourin R. Aura

Abstract — In this study, a new general expression for the frequency of a SERO is constructed, which includes two additional variables, K<sub>d</sub> and R<sub>w</sub>, and improves upon the traditional equations by accounting for all analysis models and various width ratios. When compared with the the conventional equations, the proposed equation is a better alternate to study the frequency response when the width ratio is concerned parameter for researchers which is addressed by the variable Rw. A three stage SERO is simulated in 90 nm technology using Cadence Virtuoso platform to establish this equation. The value of K<sub>d</sub> obtained remains almost equal which justifies the reason for using this approach traditionally to calculate the delay.

Keywords — frequency; propagation delay; single ended ring oscillator; voltage controlled oscillator.

# I. INTRODUCTION

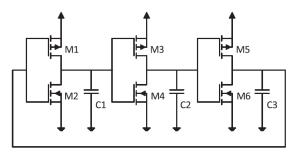

Voltage controlled oscillator (VCO) is an important element in the communication system and digital electronics for essential tasks such as frequency selection and clock signal generation [1,2]. Single ended ring oscillator (SERO) has been a popular choice for VCO over the inductorcapacitor (LC) oscillator because of its benefits in terms of simple manufacturability, smaller area and wider frequency tuning range [3]. A conventional SERO consists of an odd number of CMOS inverter stages as shown in Fig. 1. The load capacitances of each stage due to the MOSFET parasitics are also shown in Fig. 1.

Fig. 1. Conventional SERO with load capacitances.

The expression of oscillating frequency in a RO is given by (1), which shows that the frequency is inversely proportional to the number of delay stages N and propagation delay t<sub>pd</sub> at each stage [4]. The propagation delay t<sub>pd</sub> is an average of the high-to-low and low-to-high propagation delays,  $t_{dHL}$  and  $t_{dLH}$  respectively [5]. Equation (1) can then be written as in (2).

$$f_{osc} = \frac{1}{2Nt_{pd}}$$

(1)

Submitted on July 08, 2022.

Published on August 03, 2022.

S.R. Aura, Ahsanullah University of Science & Technology, Bangladesh. (e-mail: aura.eee@aust.edu)

$$f_{osc} = \frac{1}{N(t_{dHL} + t_{dLH})}$$

(2)

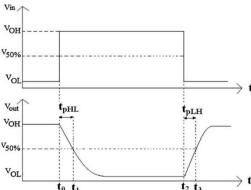

Therefore, in order to analyze and estimate the frequency of oscillation, it is essential to correctly model the propagation delays  $t_{dHL}$  and  $t_{dLH}$  [6]. Two conventional methods exist to determine an approximate delay equation which analyze the CMOS inverter circuit differently. In the first method, the transistors are modelled as current sources with a constant current supply which charges and discharges the load capacitance C<sub>L</sub> [7]. In the second method, the transistor is modeled as a resistor and an equivalent RC circuit is solved for the delay expression [8]. The point at which the delay is calculated can also vary and result in a similar equation with a different coefficient value. The propagation delay can be calculated when the output is at either 50%, 90% or 100% level of the supply voltage. Although the delay is calculated at the 50% level conventionally, as shown in Fig. 2, some equations mentioned in literature [9,10] have considered the 90% and 100% levels.

Fig. 2. Propagation delay calculation at 50% level.

These analyses can lead to 5 different frequency equations for a single circuit. Moreover, the equations are based on the assumption that the PMOS to NMOS width ratio, W<sub>p</sub>/W<sub>n</sub> is 2. The objective of this paper is to present the analytical derivations of all these 5 equations not available in literature and, hence, derive a new general expression for the frequency of an SERO which takes into account all analysis models and different width ratios. The rest of the paper is organized as follows: section II presents the derivation of the frequency equation based on different models, section III presents the proposed general expression and simulation results are presented in section IV. Finally, section V concludes the paper while providing insight to future scope.

#### II. CONVENTIONAL FREQUENCY EQUATIONS

# A. Current Source (CS) Model

# 1) Delay at 50% level

As mentioned before, one way to model the propagation delay is by assuming the transistors as current sources which charge and discharge the load capacitance. The charging and discharging current equations are then given by:

$$C_{L} \int_{0}^{\underline{V_{DD}}} dV_{out} = \int_{0}^{t_{dLH}} I_{p} dt$$

(3)

$$C_L \int_{V_{DD}}^{\frac{V_{DD}}{2}} dV_{out} = -\int_0^{t_{dHL}} I_n dt$$

(4)

where, I<sub>n</sub> and I<sub>p</sub> are saturation currents of NMOS and PMOS transistors, respectively. The propagation delays tdLH and tdHL are obtained as (5) and (6). Assuming,  $W_p/W_n = 2$ and, hence,  $I_n = I_p = I_s$ , the resultant frequency equation is obtained in (7), where I<sub>s</sub> is the current through a single delay stage.

$$t_{dLH} = \frac{V_{DD}C_L}{2I_p} \tag{5}$$

$$t_{dHL} = \frac{V_{DD}C_L}{2I_n} \tag{6}$$

$$f_{\rm osc} = \frac{I_{\rm S}}{NV_{\rm DD}C_{\rm L}} \tag{7}$$

# 2) Delay at 90% level

For the delay calculation at 90% level, the integral limits are changed from  $V_{DD}/2$  to  $0.9V_{DD}$  and  $0.1V_{DD}$  in equation (3) and (4), respectively. Equations (5) and (6) then change to equations (8) and (9). The resultant frequency then obtained is given by (10).

$$t_{dLH} = \frac{0.9V_{DD}C_L}{L} \tag{8}$$

$$t_{dLH} = \frac{0.9V_{DD}C_L}{I_p}$$

$$t_{dHL} = \frac{0.9V_{DD}C_L}{I_n}$$

(8)

$$f_{\rm osc} = \frac{I_{\rm S}}{1.8NV_{\rm DD}C_{\rm I}} \tag{10}$$

### 3) Delay at 100% level

For the 100% level, the delay is calculated when the output reaches the voltage rails, V<sub>DD</sub> or 0. In a similar method as before, the integral limits are now from 0 to  $V_{DD}$  and  $V_{DD}$  to 0 for equations (3) and (4), respectively. The propagation delays then obtained are given by (11) and (12) which leads to the frequency equation given by (13). This is the most common equation in literature.

$$t_{dLH} = \frac{V_{DD}C_L}{I_p} \tag{11}$$

$$t_{dHL} = \frac{V_{DD}C_L}{I_n}$$

(12)

$$f_{\rm osc} = \frac{I_{\rm S}}{2NV_{\rm DD}C_{\rm L}} \tag{13}$$

#### B. RC Model

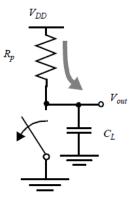

As mentioned in section 1, the inverter can also be modelled as an RC network to obtain the propagation delay. Suppose, C<sub>L</sub> is being charged to a voltage V<sub>out</sub> from supply voltage  $V_{DD}$  when  $V_{in} = 0$ , as shown in Fig. 3. The operation of the network is described by the following differential equation [11]:

$$C_L \frac{dV_{out}}{dt} + \frac{V_{out} - V_{in}}{R_n} = 0$$

(14)

where, R<sub>p</sub> is the equivalent PMOS resistance. The output expression is given by (15).

$$V_{\text{out}} = \left(1 - e^{-\frac{t_{\text{dLH}}}{R_{\text{p}}C_{\text{L}}}}\right) V_{\text{DD}} \tag{15}$$

Fig. 3. RC model of CMOS inverter at  $V_{\rm in} = 0$ .

# 1) Delay at 50% level

For calculating delay at 50% voltage level,  $V_{out} = 0.5V_{DD}$ and the expression of t<sub>dLH</sub> obtained is given by (16). Similarly for the discharging scenario, the expression of t<sub>dHL</sub> is given by (17), where  $R_n$  is the equivalent NMOS resistance.

$$t_{dLH} = \ln(2) R_p C_L \tag{16}$$

$$t_{dHL} = \ln(2) R_n C_L \tag{17}$$

The average on-resistances  $R_n$  and  $R_p$  can be calculated by integrating the I-V characteristic curves of the NMOS and PMOS, respectively, over the interval of interest. For example, for 50% delay calculation, the expression of R<sub>p</sub> is given by (18) where  $\lambda$  is the channel length modulation constant for short channel devices. Assuming  $\lambda = 0$ , the approximate expressions of  $R_p$  and  $R_n$  are given by (19) and (20).

$$R_{p} = \frac{1}{-\frac{V_{DD}}{2}} \int_{V_{DD}}^{\frac{V_{DD}}{2}} \frac{V dV}{I_{p}(1 + \lambda V)}$$

$$\approx \frac{3V_{DD}}{4I_{p}} (1 - \frac{7}{9} \lambda V_{DD})$$

(18)

$$R_{p} = \frac{3V_{DD}}{4I_{p}} \tag{19}$$

$$R_n = \frac{3V_{DD}}{4I_n} \tag{20}$$

Substituting equations (19) and (20) in (16) and (17), the resulting frequency equation is given by (21) where  $I_s = I_n =$  $I_p$ , assuming  $W_p/W_n = 2$ .

$$f_{\rm osc} = \frac{I_{\rm S}}{1.5\ln{(2)}NV_{\rm DD}C_{\rm L}} \tag{21}$$

#### 2) Delay at 90% level

For calculating delay at 90% voltage level,  $V_{out} = 0.9V_{DD}$ in equation (15) and the delay expressions obtained are given by (22) and (23).

$$t_{dLH} = \ln(10) R_p C_L \tag{22}$$

$$t_{\rm dHL} = \ln(10) R_{\rm n} C_{\rm L} \tag{23}$$

The equivalent average on-resistances  $R_n$  and  $R_p$  are now calculated within the limits 0 and  $V_{\text{DD}}$  and the expressions are given by (24) and (25), respectively. Substituting (24) and (25) in (22) and (23), the resulting frequency expression obtain is given by (26).

$$R_{n} \approx \frac{V_{DD}}{I_{n}} \tag{24}$$

$$R_{\rm p} \approx \frac{V_{\rm DD}}{I_{\rm p}} \tag{25}$$

$$f_{\rm osc} = \frac{I_{\rm S}}{2\ln(10)\,\text{NV}_{\rm DD}C_{\rm L}} \tag{26}$$

Note that, using the RC model, the delay cannot be calculated at the 100% voltage level as the value of t<sub>dLH</sub> from (15) evaluates to 0.

# III. PROPOSED GENERAL EQUATION

The objective of this work is to present all 5 equations discussed above into one single equation while addressing the variable  $W_p/W_n$  ratio in the expression. Let  $W_p = R_wW_n$ , where R<sub>w</sub> is the PMOS transistor to NMOS transistor width ratio. Since the frequency equations consist of the current Is, a relation between  $I_n$  and  $I_p$  in terms  $R_w$  needs to be developed. Ideally when  $R_w = 2$ ,  $I_n = I_p = I_s$ , and when  $R_w = 1$ ,  $I_n = 2I_p$ . This is due to the difference in mobility of electrons and holes in NMOS and PMOS, respectively. Therefore, the relation between  $I_n$  and  $I_p$  is given by (27).

$$I_{n} = \frac{2}{R_{w}} I_{p} \tag{27}$$

Using this relation with the CS model and 50% delay calculation procedure, the high-to-low and low-to-high propagation delays obtained are given by:

$$t_{dHL} = \frac{C_L V_{DD}}{2I_p \frac{2}{R}} = \frac{R_w C_L V_{DD}}{4I_p}$$

(28)

$$t_{dLH} = \frac{C_L V_{DD}}{2I_p} \tag{29}$$

The summation of the two delays, t<sub>d</sub> is given by equation (30).

$$t_d = t_{dHL} + t_{dLH}$$

$$= \frac{2C_{L}V_{DD} + R_{w}C_{L}V_{DD}}{4I_{p}}$$

(30)

$$=\frac{C_{\rm L}V_{\rm DD}(1+0.5R_{\rm w})}{2I_{\rm p}}$$

Using equation (30), the expression of oscillating frequency for the 50% CS model is given by (31) where, K<sub>d</sub> is the coefficient of delay model and Is is the source current.  $K_d$  is 0.5 in this case. Since,  $I_p$  is directly the current from the supply, I<sub>p</sub> can be replaced with I<sub>s</sub>.

$$f_{osc} = \frac{I_s}{K_d(1 + 0.5R_w)NC_L V_{DD}}$$

(31)

Similarly, the relation in (27) can be used for the remaining 4 models to obtain the same expression in (31) for the frequency but with different K<sub>d</sub> value. The value of coefficient for the 5 different models are presented in Table I.

TABLE I: VALUE OF COEFFICIENT KD FOR DIFFERENT MODELS

| Model   | $K_{d}$ |

|---------|---------|

| 50% CS  | 0.50    |

| 50% RC  | 0.52    |

| 90% CS  | 0.90    |

| 100% CS | 1.00    |

| 90% RC  | 2.30    |

# IV. SIMULATION RESULTS

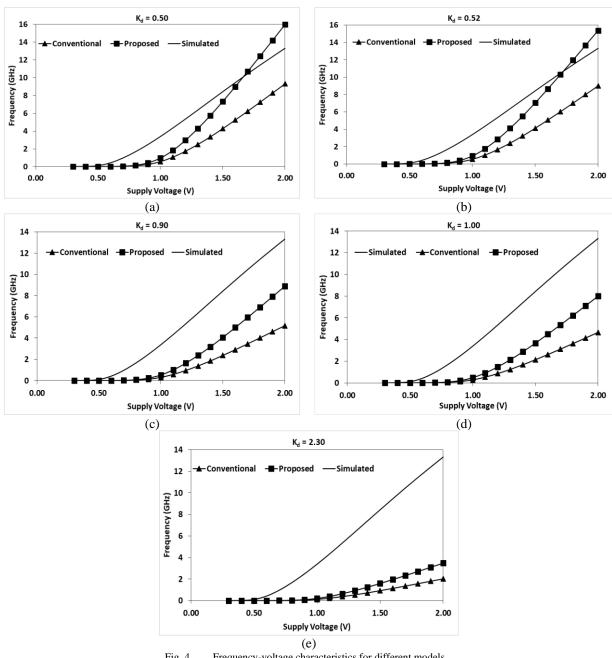

A three stage SERO with load capacitances is simulated in 90 nm technology using Cadence Virtuoso platform. The supply voltage is varied between 0.3 V and 2 V. The value of the load capacitance is calculated using the equation in [12]. The circuit is first simulated with  $R_w = 2$  and the new equation is compared with the conventional equations. The percentage of error between the proposed and existing equations for all values of V<sub>DD</sub>, as given in Table II, shows that the proposed expression obtains the same result as the conventional equations when the width ratio is 2.

TABLE II: PERCENTAGE ERROR OF FREQUENCY

| Model  | 50% CS | 50% RC | 90% CS | 100% CS | 90% RC |

|--------|--------|--------|--------|---------|--------|

| Error* | 0      | -0.48  | 0      | 0       | 0      |

| (%)    |        |        |        |         |        |

\*

$$Error = \frac{F_{new} - F_{conv}}{F_{conv}} \times 100$$

The circuit is re-simulated with  $R_{\rm w} = 0.33$  where  $W_{\rm n} = 360$ nm and  $W_p = 120$  nm. The simulated frequency response is then compared with both conventional and proposed equation models. The different frequency-voltage characteristics shown in Fig. 4 proves that the proposed equation gives a better estimation (71% improvement) of the frequency since it addresses the changed width ratio.

#### V. CONCLUSIONS AND FUTURE SCOPES

The analytical frequency equation of an SERO can be obtained through various approaches leading to different results. The conventional methods also assume the ideal value of 2 for the PMOS to NMOS width ratio. A new general expression is proposed in this paper which introduces two new variables Kd and Rw. The value of Kd is given in Table 1 for different delay models which may be chosen for the frequency estimation. The variable Rw addresses the effect of PMOS to NMOS width ratio on the frequency and provides 71% improvement than the conventional equations. Therefore, the proposed equation is a better alternate to the conventional equations to study the frequency response when the width ratio is concerned parameter for researchers. Using the 50% delay calculation for both CS and RC models, the value of Kd obtained remains almost equal which justifies the reason for using this approach traditionally to calculate the delay. In future, the effectiveness of the equation can be studied for more different width ratios and technologies. Although the proposed equation proves to be a better alternative, the percentage of errors with the simulated frequency response remain very high. This is because the current and load capacitance were assumed constant, though they are both voltage dependent. The MOSFETs' region of operation also changes during one voltage swing which changes the expressions of current and equivalent resistance. The current and load capacitance also need to be simulated

Fig. 4 Frequency-voltage characteristics for different models.

and calculated, respectively, to estimate the frequency which makes the equation futile for designers. A more accurate, while simple, frequency equation needs to be derived in future for reliable study of the RO frequency response.

#### REFERENCES

- [1] Demir A., Mehrotra A., Roychowdhury J. Phase noise in oscillators: a unifying theory and numerical methods for characterization. IEEE Trans Circuits Syst I Fundam Theory Appl, 2000;47(5):655-74.

- [2] Mal S., Mal A.K., Ghosh S. Voltage-controlled ring oscillator for harmonic frequency generation. In: Advances in Intelligent Systems and Computing (ICA), p. 277-86.

- Ishraqul H., Apratim R. Relative Design Merits and Trends in Single-Ended Ring Voltage Controlled Oscillators. IETE Journal of Research, Aug. 2019.

- [4] Gagandeep S., Mandeep S. A. Design of wide tuning range and low power dissipation of VCRO in 50 nm CMOS Technology. International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, May 2014, 3(5):9675-79.

- [5] Jubayer J., Mamun B. I. R., Mohd A. M. A., CMOS differential ring oscillators: Review of the Performance of CMOS ROs in Communication Systems. IEEE Microwave Magazine, 2013;12(5): 97-

- [6] Elnaz Z., Mohammad M., Maryam Z., Improved accuracy equation for propagation delay of a CMOS inverter in a single ended ring oscillator. International Journal of Electronics and Communications (AEÜ), 2017:71:110-117.

- [7] Abidi A. A. Phase noise and jitter in CMOS ring oscillators. IEEE Journal of Solid-State Circuits, 2006; 41(8):1803-16.

- Felipe S. M., André I. S., Renato P. R., CMOS inverter delay model based on DC transfer curve for slow input. 14th International Symposium on Quality Electronic Design (ISQED), pp. 651-7. B, June 2013.

- Stephen D. A Method to Derive an Equation for the Oscillation Frequency of a Ring Oscillator. MASc. Thesis. Waterloo, Ontaria, Canada, 2002.

- [10] Bhawika K., Shruti S., Sharma K. G. & Ghosh P. K., Design of Improved Performance Voltage Controlled Ring Oscillator. 2015 Fifth International Conference on Advanced Computing & Communication Technologies.

- [11] Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolic. Digital integrated circuits: A design perspective. 2nd ed. In: Prentice hall electronics and VLSI series, 2002.

- [12] S. M. Ishraqul H., Apratim R., Design of a Linearized Split-Load Low Power Single-Ended Ring Oscillator with High Tuning Range. International Conference on Innovation in Engineering and Technology (ICIET), 23-24 December, 2019.